Author: Denis Avetisyan

Researchers have developed a reinforcement learning framework that automates the design of complex analog and mixed-signal circuits, leveraging simulation feedback for optimized performance.

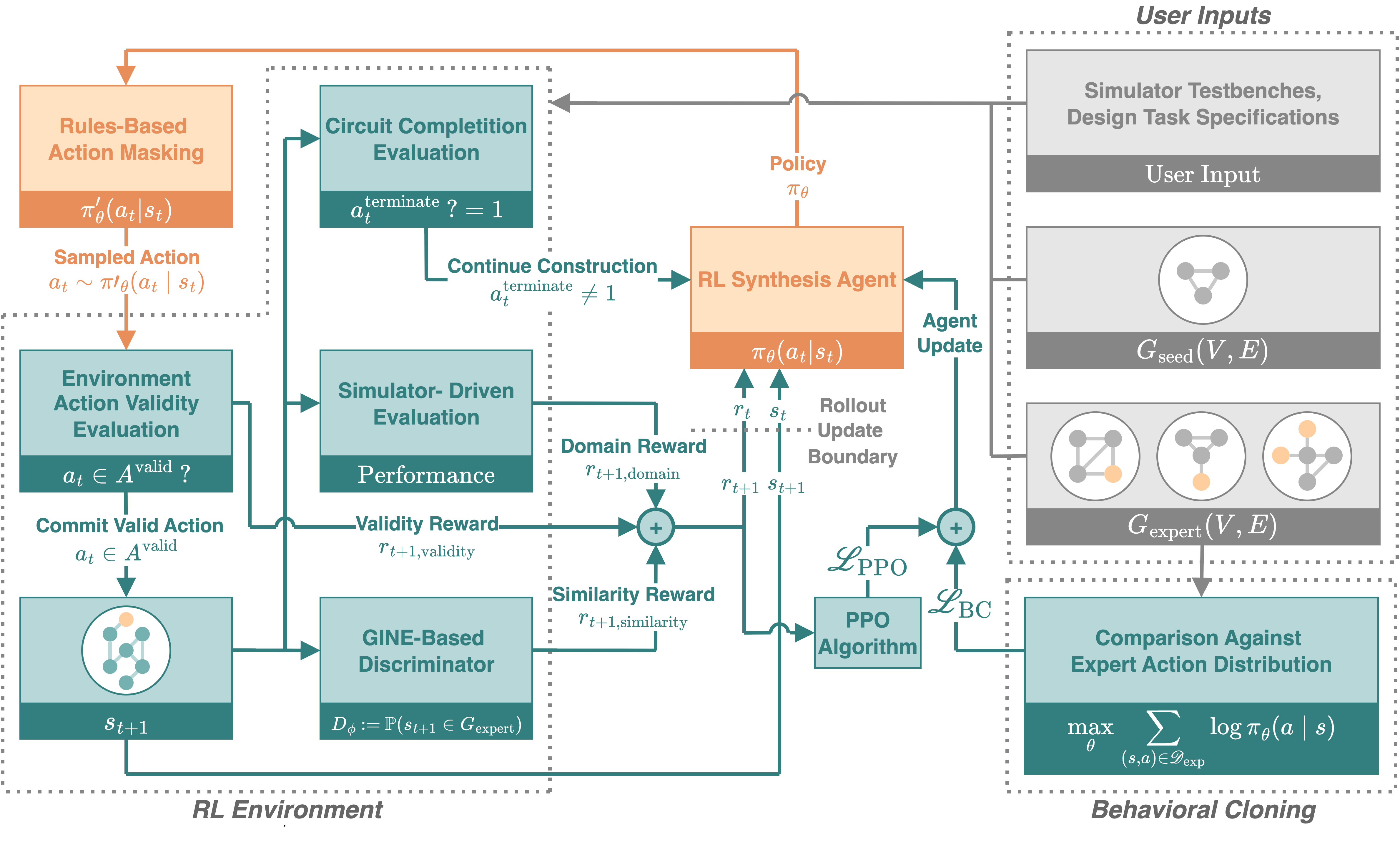

AstRL formulates circuit synthesis as a graph generation problem, utilizing deep reinforcement learning and a symmetry-aware action space for robust topology design.

Despite the increasing complexity of modern computing and communications systems, automated design techniques for analog and mixed-signal (AMS) integrated circuits have lagged, hindered by the challenges of optimizing across diverse, non-differentiable design spaces. This work introduces AstRL-AstRL: Analog and Mixed-Signal Circuit Synthesis with Deep Reinforcement Learning-a novel framework that casts AMS circuit design as a graph generation problem solvable through deep reinforcement learning within a simulator-embedded environment. AstRL achieves, for the first time, expert-aligned, generalized circuit generation by directly optimizing for user-specified targets at the transistor level, leveraging behavioral cloning and similarity rewards. Could this approach unlock a new era of rapid, automated design for increasingly sophisticated analog and mixed-signal systems?

The Inherent Challenges of Analog Circuit Synthesis

The creation of mixed-signal analog and digital systems, commonly known as AMS circuit design, presents a formidable engineering hurdle. Unlike digital circuits which operate with discrete values, analog circuits deal with continuous signals, demanding a deep understanding of device physics and circuit behavior. Successfully integrating these two domains requires expertise in both areas, a skillset increasingly rare and demanding significant time investment. This complexity isn’t merely theoretical; achieving optimal performance – low power consumption, high speed, minimal noise – while simultaneously satisfying physical layout constraints necessitates iterative design, simulation, and refinement. Consequently, bringing a new AMS circuit to fruition often requires months, even years, of dedicated effort from highly specialized engineers, creating a bottleneck in the development of cutting-edge technologies.

Conventional approaches to analog and mixed-signal (AMS) circuit design face inherent difficulties when attempting to balance competing priorities. Achieving high performance – such as speed, low power consumption, and minimal noise – typically requires intricate component selection and precise tuning, processes that become exponentially more challenging as circuit complexity increases. Simultaneously, modern integrated circuits must adhere to strict physical constraints dictated by manufacturing limitations and chip size. These constraints impact component placement, routing, and parasitic effects, creating a complex interplay between electrical performance and physical realization. Consequently, designers often resort to iterative, manual adjustments, a time-consuming process that struggles to explore the vast design space effectively and frequently results in sub-optimal solutions that either compromise performance or fail to meet physical requirements.

Contemporary automated design tools for analog-mixed signal (AMS) circuits frequently fall short of meeting the demands of modern integrated circuit development. These tools often rely on pre-defined templates or limited optimization algorithms, creating bottlenecks when faced with novel specifications or stringent performance goals. The inflexibility hinders exploration of diverse design possibilities and makes it difficult to simultaneously satisfy complex requirements like low power consumption, high speed, and minimal area. Consequently, designers are forced to rely heavily on manual intervention, a time-consuming process that limits the rate of innovation and increases development costs, particularly as feature sizes shrink and circuit complexity escalates. The inability of existing tools to efficiently navigate this intricate design space ultimately constrains the advancement of cutting-edge electronic systems.

Current automated circuit generation techniques, while offering some assistance, ultimately fall short of addressing the intricate demands of modern analog and mixed-signal system design. These methods frequently prioritize performance metrics in isolation, neglecting the crucial interplay with physical layout and manufacturing constraints – a disconnect that leads to designs impractical for real-world implementation. Consequently, a fundamental shift is needed, moving beyond incremental improvements to embrace a completely new design paradigm. This novel approach must intrinsically integrate performance optimization with physical awareness, leveraging techniques such as co-design and machine learning to automatically generate circuits that are not only high-performing but also readily manufacturable and scalable, thereby unlocking a new era of innovation in integrated circuit development.

AstRL: A Graph-Theoretic Formulation for Circuit Synthesis

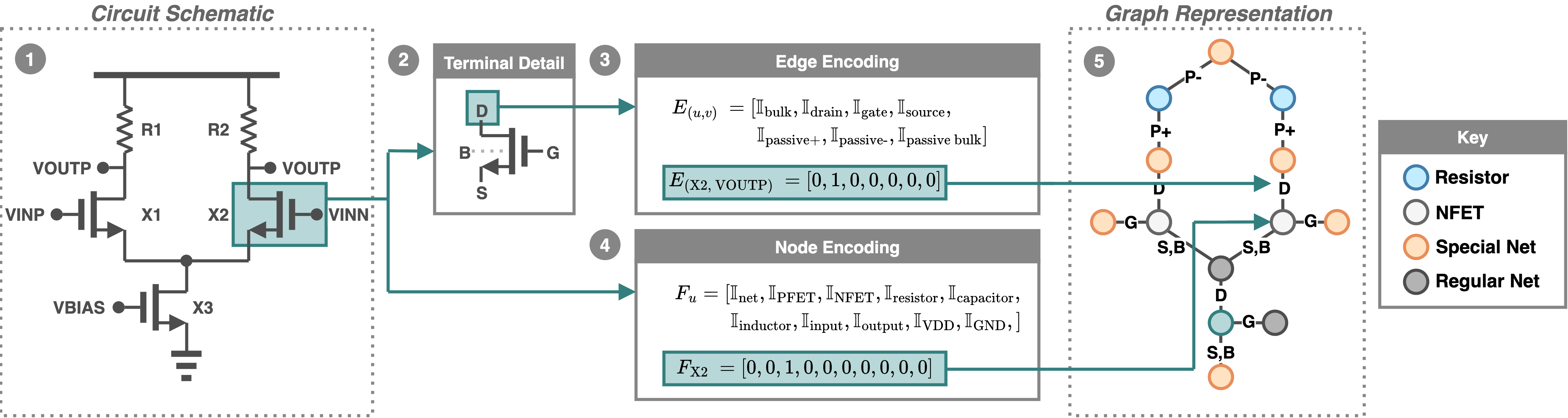

AstRL represents circuit topologies as graphs, where nodes represent circuit elements and edges define their interconnections. This graph-based representation facilitates the incorporation of structural inductive biases, allowing the model to prioritize valid and physically realizable circuit configurations during the learning process. Utilizing graph representations enables efficient learning through the application of graph neural networks and graph convolution operations, which can effectively capture the relationships between circuit components and generalize across different circuit designs. This approach contrasts with methods relying on flattened or rasterized representations, as it explicitly encodes the inherent structural properties of circuits, leading to improved sample efficiency and performance.

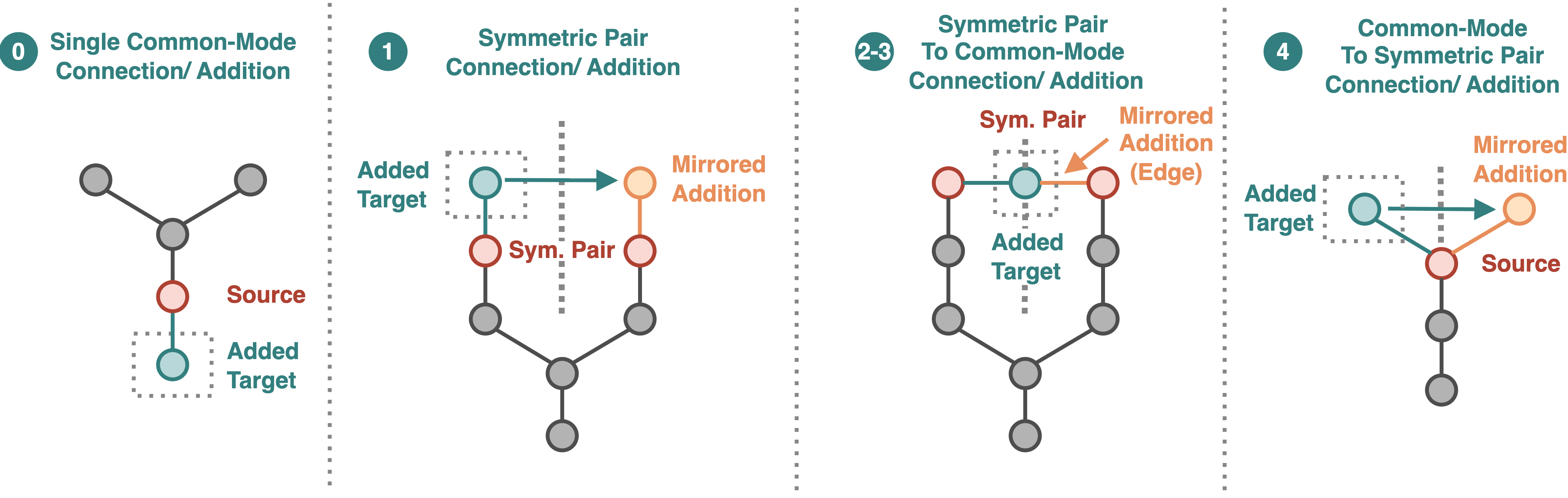

The AstRL system leverages a policy gradient method, specifically utilizing reinforcement learning to iteratively construct circuit graphs. This process involves an agent that sequentially adds components to a growing circuit topology, with each action determined by a parameterized policy. The policy is updated based on the observed performance of the generated circuit, calculated against specified performance metrics. The gradient of the expected reward is estimated through Monte Carlo sampling, and this gradient is used to adjust the policy parameters, encouraging the generation of circuits with higher rewards. This sequential generation approach allows AstRL to explore a broad design space and optimize for multiple, potentially conflicting, objectives without requiring a predefined circuit structure.

The reward function within AstRL is a weighted sum of three primary components designed to effectively guide the reinforcement learning agent. Simulation Validity assesses the physical realism of the generated circuit, penalizing designs that violate fundamental physical laws or produce unstable simulations. Specification Fulfillment measures the degree to which the circuit meets the desired performance criteria, such as target frequency response or power consumption. Finally, Circuit Complexity introduces a penalty for overly complex designs, encouraging the agent to favor simpler solutions that achieve comparable performance. The relative weights assigned to each component are hyperparameters tuned to balance these competing objectives and achieve optimal circuit generation.

Behavioral cloning is integrated into the AstRL framework to address the challenges of exploration inherent in reinforcement learning. This technique leverages a dataset of expert-designed circuits to pre-train the policy network via supervised learning, effectively initializing it with a strong prior. By mimicking expert behavior, the agent begins the reinforcement learning process with a functional policy, significantly reducing the time required for exploration and accelerating convergence. Furthermore, behavioral cloning improves initial performance by providing a solid starting point, allowing the agent to quickly achieve reasonable results and avoid the potentially slow and unstable learning associated with random initialization. This approach combines the benefits of supervised learning – faster initial progress – with the adaptability of reinforcement learning for further optimization.

Ensuring Syntactic and Functional Correctness Through Constraints

Structural constraints are implemented during the initial graph construction phase to ensure the generated circuit topologies adhere to fundamental electronic design rules and physical limitations. These constraints govern node connectivity, transistor sizing, and power supply connections, preventing the creation of invalid or unrealizable circuit configurations. Specifically, the framework restricts the number of inputs and outputs per node, limits fan-out based on transistor drive strength, and enforces proper grounding and power distribution. By proactively addressing these limitations at the graph level, the system guarantees that all subsequently generated netlists represent physically plausible circuits suitable for simulation and potential fabrication, thereby eliminating invalid designs before significant computational resources are expended.

Symmetric Action Modifiers are incorporated into the circuit generation process to enhance performance and reduce the computational search space. These modifiers encourage the creation of circuit topologies exhibiting symmetry, a characteristic often associated with improved electrical characteristics and reduced complexity. By biasing the reinforcement learning agent towards symmetric designs, the framework explores a smaller, more promising subset of the total possible circuit configurations. This approach leverages the principle that symmetry can simplify analysis and optimization, leading to faster convergence and potentially superior circuit performance compared to purely random exploration.

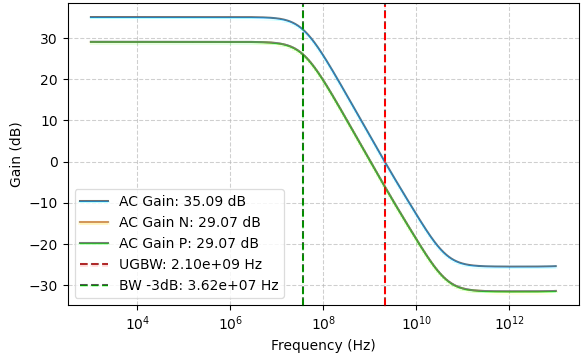

Evaluation of the AstRL framework utilized the Skywater 130nm process design kit (PDK), a widely adopted open-source silicon technology. This CMOS process features a minimum feature size of 130 nanometers and is supported by comprehensive simulation models and design tools, facilitating both circuit simulation and physical layout for fabrication. The Skywater 130nm PDK was selected for its accessibility and standardization within the research community, enabling reproducible results and facilitating comparison against other published works employing the same technology node. Use of this established PDK ensures the generated circuits are realistically implementable and verifiable using industry-standard Electronic Design Automation (EDA) software.

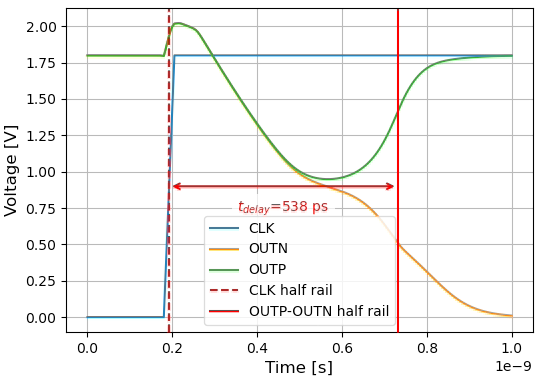

Evaluation of the AstRL framework successfully generated valid circuit netlists for a diverse set of analog designs, including Operational Transconductance Amplifiers (OTA), Comparators, and Ring Oscillators. Across all generated designs, 100% of the resulting netlists adhered to standard circuit syntax and were structurally correct, indicating successful translation of the generated graph representation into a physically realizable circuit description. This validation confirms the framework’s ability to consistently produce syntactically and structurally valid circuits across different topologies.

Comparative analysis demonstrates that the AstRL framework achieves enhanced performance metrics relative to existing circuit generation methodologies. Specifically, the framework yielded a statistically significant increase in simulation validity, indicated by a higher percentage of generated netlists successfully completing simulations without errors. Furthermore, specification fulfillment-defined as the degree to which generated circuits meet predefined performance criteria-was also demonstrably improved. Quantitative results show a consistent advantage across a range of circuit types and complexity levels, confirming the framework’s ability to produce both functionally correct and high-performing designs compared to state-of-the-art approaches.

Toward a Future of Automated Circuit Innovation

AstRL represents a significant advancement in automated circuit design by building upon, and ultimately surpassing, the capabilities of established methodologies like AnalogCoder and AnalogGenie. While previous approaches often relied on predefined templates or limited optimization strategies, AstRL employs a reinforcement learning framework that enables it to explore a vastly larger design space. This innovative approach doesn’t merely refine existing circuits; it generates entirely new topologies, often achieving superior performance metrics in simulations. Independent evaluations demonstrate that AstRL consistently produces circuits with improved power efficiency, reduced area, and enhanced stability compared to those created by its predecessors, suggesting a pathway toward more complex and optimized analog and mixed-signal systems.

The AstRL framework distinguishes itself through a remarkable capacity for adaptability, enabling designers to swiftly generate and evaluate a diverse range of circuit configurations. This agility stems from the system’s ability to respond to varying design specifications and constraints, facilitating rapid prototyping that would be impractical with traditional methods. Researchers can explore previously unconsidered circuit architectures with relative ease, iterating on designs and optimizing performance metrics at an accelerated pace. The framework’s inherent flexibility doesn’t simply refine existing designs; it empowers a more expansive investigation of the design space, potentially uncovering innovative solutions and pushing the boundaries of circuit performance and efficiency. This capacity for exploration promises to reshape the future of circuit design, moving beyond incremental improvements towards genuinely novel technological advancements.

The advent of automated circuit design promises a transformative shift in technological development, potentially compressing years of painstaking manual effort into weeks or even days. This acceleration stems from the ability of systems to rapidly generate, simulate, and optimize circuit layouts, freeing engineers to focus on higher-level system architecture and innovation. Beyond simply speeding up the process, automation unlocks the exploration of previously inaccessible design spaces, allowing for the discovery of novel and highly efficient circuits tailored to specific applications – from low-power mobile devices to high-performance computing systems. This capability isn’t limited to electronics; breakthroughs in automated circuit design can drive progress in fields as diverse as robotics, medical devices, and renewable energy, fostering a new era of rapid prototyping and technological advancement.

Continued development of automated circuit design frameworks centers on addressing the intricacies of real-world engineering challenges. Current research prioritizes the integration of more complex design constraints, such as considerations for power consumption, noise immunity, and manufacturing variability, to produce circuits that are not only functional but also robust and efficient. Furthermore, optimization efforts are expanding beyond traditional metrics like speed and area, now encompassing performance characteristics like linearity, stability, and signal-to-noise ratio. This multifaceted approach promises to unlock increasingly sophisticated circuit topologies tailored to specific application requirements, ultimately accelerating innovation across diverse technological landscapes and enabling the creation of high-performance, specialized systems.

The presented AstRL framework embodies a commitment to provable solutions, mirroring Ken Thompson’s observation that “Software is only ever 99% perfect, and that 1% can cause a lot of problems.” AstRL doesn’t merely seek circuits that work based on simulation; it formulates design as a graph generation problem, enabling a systematic exploration of the design space. This approach, fueled by reinforcement learning and informed by simulator feedback, strives towards robust optimization-a demonstrable correctness that extends beyond superficial functionality. The symmetry-aware action space, a key component of the methodology, further reinforces this dedication to mathematical elegance and verifiable results within the realm of analog and mixed-signal circuit design.

What Remains to be Proven?

The presented framework, AstRL, achieves a demonstrable synthesis of analog and mixed-signal circuits, a feat not to be dismissed. However, the inherent stochasticity of reinforcement learning invites scrutiny. While simulator feedback guides optimization, the convergence to a globally optimal topology remains, at best, a probabilistic assertion. Future work must address the question of provable optimality-can invariants be established to guarantee a solution within a defined error bound, or is the field destined for an endless refinement of ‘good enough’ designs?

A critical limitation lies in the scalability of the graph generation process. The complexity of AMS circuits grows non-linearly with specifications. Current approaches, reliant on brute-force exploration of the action space, will inevitably encounter asymptotic bottlenecks. A promising direction involves the incorporation of formal methods – perhaps leveraging symbolic circuit analysis – to prune the search space and guide the agent toward solutions with mathematically verifiable properties.

Finally, the symmetry-aware action space, while an improvement, merely mitigates, rather than eliminates, redundancy. True elegance demands a solution that is not simply ‘better by chance’, but fundamentally minimal. A deeper investigation into the application of information-theoretic principles – quantifying the ‘information content’ of a circuit topology – may offer a path toward truly optimal designs, where every component serves a demonstrably necessary function.

Original article: https://arxiv.org/pdf/2602.12402.pdf

Contact the author: https://www.linkedin.com/in/avetisyan/

See also:

- 2025 Crypto Wallets: Secure, Smart, and Surprisingly Simple!

- Gold Rate Forecast

- Here Are the Best TV Shows to Stream this Weekend on Paramount+, Including ‘48 Hours’

- Top 15 Celebrities in Music Videos

- Top 20 Extremely Short Anime Series

- Where to Change Hair Color in Where Winds Meet

- 20 Films Where the Opening Credits Play Over a Single Continuous Shot

- Top gainers and losers

- 50 Serial Killer Movies That Will Keep You Up All Night

- 20 Must-See European Movies That Will Leave You Breathless

2026-02-16 10:07